SiFive Performance

P400

The SiFive Performance™ P450/470-Series application processors are SiFive’s first efficiency-focused Out-of-Order processors. The P400-series is derived from the successful and mature P500-Series, with considerable finely-tuned optimizations for best-in-class performance efficiency and compute density.

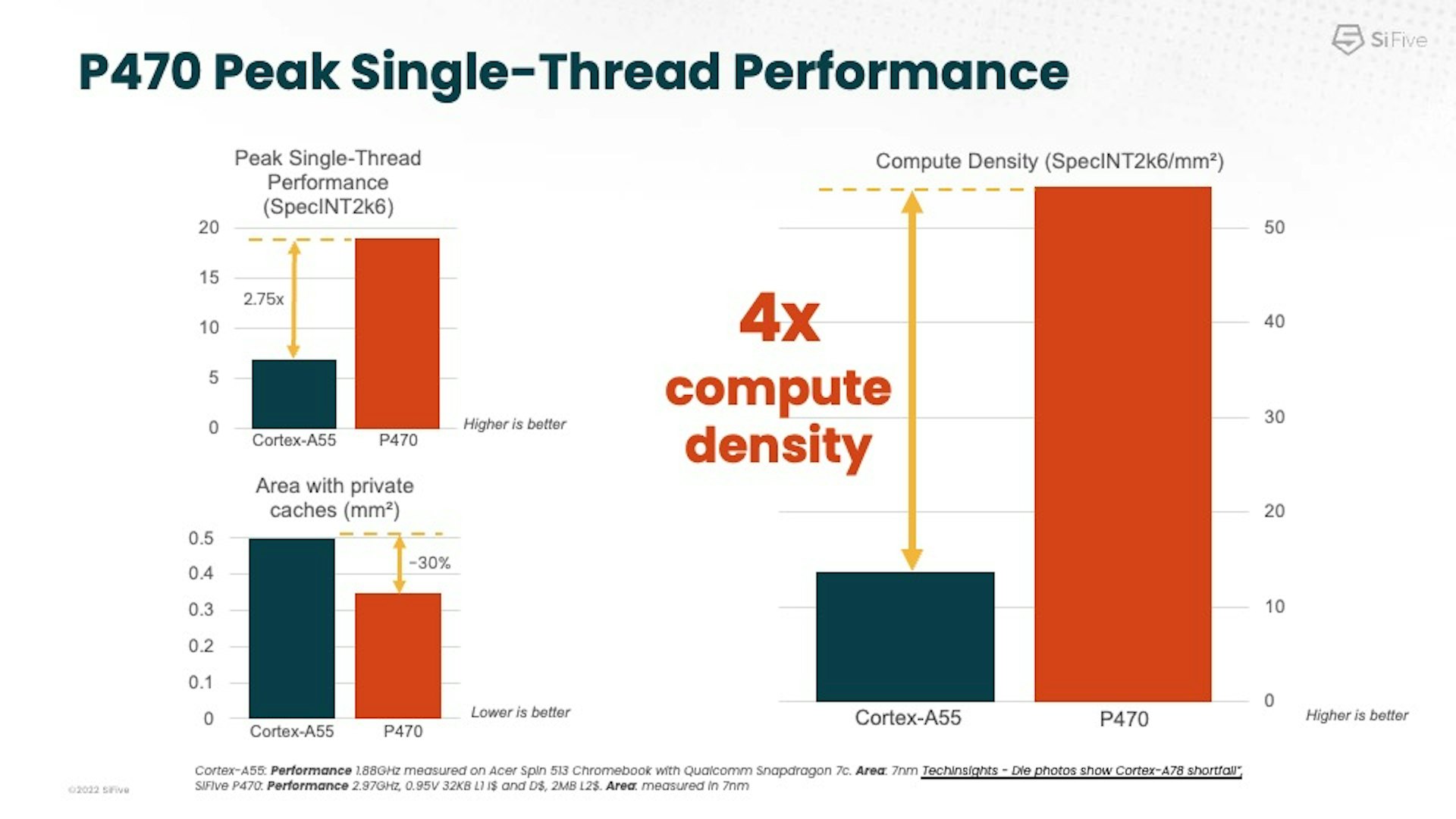

The P470 vector application processor, with a 128-bit RISC-V Vector ALU, is capable of 2x the single thread performance of an Arm Cortex-A55, achieving >8 SpecINT2k6/GHz, still within similar area and power budgets, representing a significant upgrade to legacy efficiency class cores currently available.

For applications that don't require vector compute, or for more area-constrained markets, the P450 offers similar performance levels in a smaller area footprint.

SiFive Performance Family

The SiFive Performance family of RISC-V processors is designed for maximum throughput, while preserving power efficiency for workloads as varied as branch-intensive operating systems, and multimedia processing. Ranging from 8-stage, dual-issue, in-order architectures equipped with 256-bit vector engines, to advanced three and four-issue out-of-order processors, with and without vector compute capabilities, with best-in-class industry benchmark performance, the SiFive Performance Family represents the future of compute.

SiFive Performance

P400-Series Key Features

- Full support for the RVA22 RISC-V profile specification for enabling 64-bit apps processors running feature rich OS stacks such as Linux, Wear OS, and Android.

- Best-in-class RISC-V performance efficiency

- Coherent multi-core, multi-cluster processor configuration, up to 16 cores

- Performance >8 SpecINT2k6/GHz, twice the single thread performance of the Arm® Cortex-A55® (P470 Processor)

- 1x 128-bit RISC-V Vector ALU, compliant the ratified RISC-V Vector specification as well as the (P470 Processor)

- RISC-V Vector Cryptography extension (P470 Processor) - P400-Series Architectural Features

- 64-bit RISC-V core with extensive virtual memory support

- Three issue, out-of-order pipeline tuned for scalable, highly efficient performance

- Private L2 Caches and Streaming Prefetcher for improved memory performance

- SECDED ECC with Error Reporting - Enabling next generation Wearable and Consumer applications

- Advanced interrupt controller with support for MSI style interrupts and virtualization

- System Level Virtualization IP

- Cache stashing to L3 for tightly coupled accelerators