SiFive

Automotive

E6-A

The SiFive Automotive™ E6-A series is designed for a variety of real-time, 32-bit applications, from system control to hardware security modules (HSMs) and safety islands, and of course for use as standalone in microcontrollers.

A mid-range power efficient performance 32-bit embedded processor that is fully compliant with the RISC-V ISA. Its advanced memory subsystem enables inclusion of tightly integrated memory and caches.

SiFive Automotive Family

- Broadest range of optimized RISC-V safety processors (ISO26262 ASIL B, ASIL D and split-lock)

- ADAS/AD, IVI, Body, Powertrain, Central Compute

- Safety Islands

SiFive Automotive

E6-A Features

The SiFive Automotive E6-A Series is a 32-bit RISC-V processor family, fully optimized for area, performance, and efficiency, specifically designed for the Automotive and Functional Safety markets. Building on the robust foundations of the mature SiFive Essential™ portfolio, the multi-core capable design of the E6-A Series offers industry best-in-class functional safety support as a Safety Element out of Context to enable use in applications with Automotive Safety Integrity Level (as per ISO26262) up to ASIL B and ASIL D.

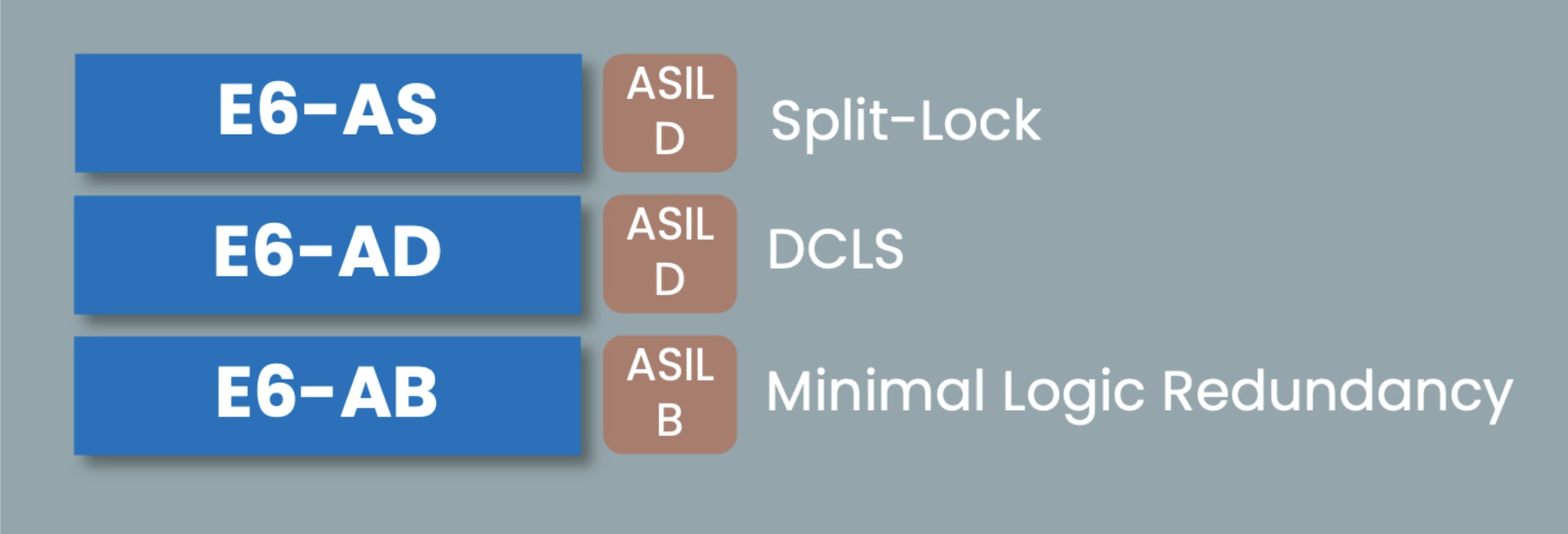

The E6-AB, targeted at ASIL B integrity levels, employs minimal hardware redundancy of the logic to guarantee safety metrics are satisfied, without the use of Software Test Libraries (STL), enabling faster time to market and minimizing software integration work.

The finely tuned combination of out-of-the-box features and design scalability ensures designers can achieve the optimal balance of power, performance, and area while achieving the fastest time to market for the automotive microcontrollers, system controllers, battery management systems (BMS), and safety island for SoC markets. In addition to the automotive market, the E6-A series is also an ideal choice for broader deployment in microcontroller applications requiring functional safety capabilities.

The E6-A Series is available in three variants; E6-AB targeting ASIL B integrity level, E6-AD targeting ASIL D integrity level, and E6-AS supporting split-lock functionality and targeting ASIL D integrity level in lock-mode.

The E6-A Series is available in three variants; E6-AB targeting ASIL B integrity level, E6-AD targeting ASIL D integrity level, and E6-AS supporting split-lock functionality and targeting ASIL D integrity level in lock-mode.SiFive Automotive E6-A Series Key

Features And Support

- 32-bit RISC-V ISA

- ASIL B and ASIL D area optimized product variants

- Functional Safety Package and Independent Assessment

- Single Issue, in-order 8-stage Harvard Pipeline

- 32-bit physical addressing

- Double, Single, and Half-precision floating point

- Configurable range of memory and SoC interface options

- Flexible and configurable Port interfaces including IO coherent interface

- Direct, dedicated Core Local Port for hardware peripheral/accelerator connectivity - WorldGuard Security

E6A

Development Kit

Dev Kit Deliverables

- RTL Evaluation

- Test Bench RTL

- Software Development Kit

- FPGA Bitstream

- Documentation